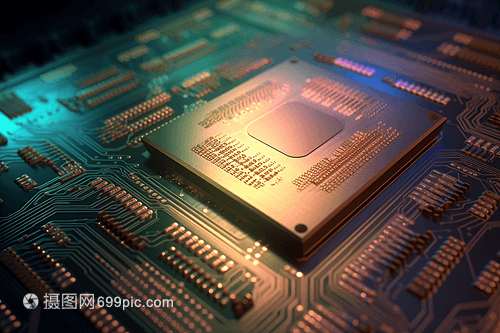

专用集成电路(ASIC)是现代电子系统的核心组件,其设计涉及多个关键技术领域,其中CMOS组合逻辑设计是基础且至关重要的环节。本文将系统介绍CMOS组合逻辑设计的基本原理、设计流程及其在集成电路中的应用。

一、CMOS组合逻辑的基本原理

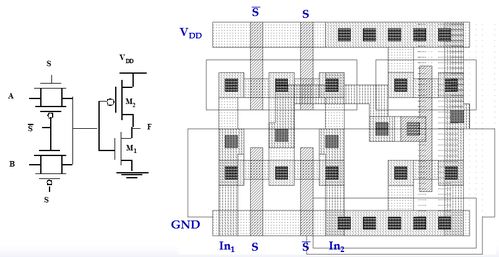

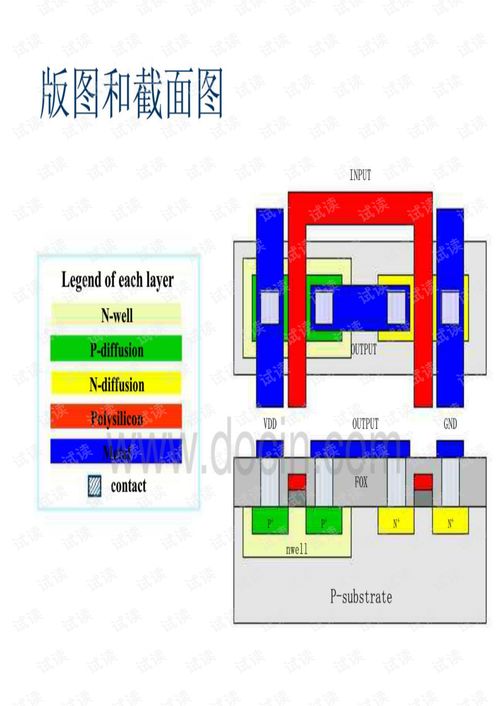

CMOS(互补金属氧化物半导体)技术因其低功耗和高集成度优势,成为当前集成电路设计的主流。组合逻辑电路的特点是输出仅取决于当前输入信号,无记忆功能。在CMOS设计中,通过NMOS和PMOS晶体管的互补组合实现逻辑功能:NMOS管用于下拉网络(传递逻辑0),PMOS管用于上拉网络(传递逻辑1)。例如,基本的CMOS反相器由一个PMOS和一个NMOS管构成,当输入为高电平时NMOS导通输出低电平,输入低电平时PMOS导通输出高电平。

二、CMOS组合逻辑的设计流程

- 逻辑功能定义:根据系统需求确定真值表或逻辑表达式。

- 电路结构设计:将逻辑表达式转化为CMOS实现结构,常用方法包括静态CMOS、传输门逻辑等。静态CMOS通过上拉网络(PMOS)实现逻辑函数的“非”形式,下拉网络(NMOS)实现原函数。

- 晶体管尺寸优化:根据速度、功耗和面积要求确定晶体管宽长比,通常需要平衡上升时间和下降时间。

- 仿真验证:使用SPICE等工具进行时序、功耗和功能仿真。

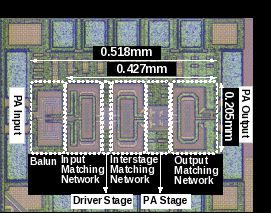

- 版图设计:按照设计规则绘制物理布局,考虑寄生参数和工艺变异影响。

三、设计关键考量因素

- 功耗控制:CMOS电路的静态功耗极低,但动态功耗与开关频率和负载电容成正比,需通过时钟门控和逻辑优化降低功耗。

- 速度优化:关键路径延迟受晶体管开关速度和互连线RC延迟影响,可通过晶体管尺寸调整和逻辑重构改善。

- 噪声容限:确保电路在电源电压波动和噪声干扰下仍能可靠工作。

- 可测试性:在设计阶段需考虑故障模型和测试策略,如扫描链插入。

四、在集成电路中的应用与发展

CMOS组合逻辑广泛用于各类ASIC中,包括算术逻辑单元(ALU)、多路选择器、编码器等模块。随着工艺进步至纳米级别,新型器件如FinFET的应用和低功耗设计技术如电源门控的引入,正在推动CMOS组合逻辑向更高性能、更低功耗方向发展。基于CMOS的可编程逻辑结构(如FPGA中的可配置逻辑块)也扩展了组合逻辑的实现灵活性。

CMOS组合逻辑设计是集成电路设计的基石,设计师需要深入理解器件特性与系统需求,通过精心优化实现性能、功耗和成本的平衡。随着异构集成和智能设计工具的发展,CMOS组合逻辑将继续在人工智能、物联网等新兴领域发挥关键作用。