在电子竞赛或教学活动中,抢答器是一种常见的设备,用于快速判断参与者的响应顺序。本文详细介绍基于74LS171集成电路的四路抢答器设计,包括器件选型、电路原理、工作过程以及实现功能。

一、设计背景与目标

抢答器广泛应用于知识竞赛、课堂互动等场景,要求能够准确记录最先按下按钮的参与者,并锁定显示结果,避免后续操作干扰。本设计采用74LS171四D触发器集成电路为核心,构建一个稳定、成本低且易于实现的四路抢答器。

二、核心器件介绍

74LS171是TTL逻辑系列的集成电路,包含四个独立的D触发器,具有公共时钟和清除功能。其引脚包括数据输入(D0-D3)、时钟输入(CLK)、清除输入(CLR)以及输出(Q0-Q3)。在抢答器中,74LS171用于存储和锁定第一个抢答信号。

三、电路设计原理

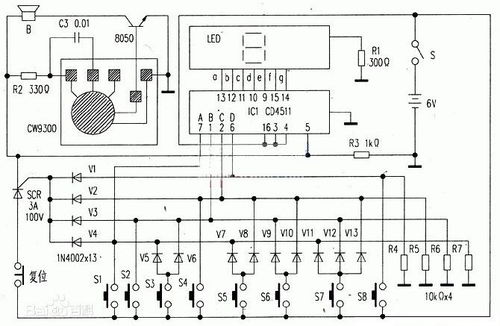

- 输入部分:四路抢答按钮(S1-S4)分别连接到74LS171的数据输入引脚(D0-D3)。按钮常态为断开状态,输入低电平;按下时提供高电平信号。

- 时钟控制:所有触发器的时钟引脚(CLK)连接在一起,通过一个公共的时钟信号控制。通常,时钟由按钮动作触发,例如使用一个或门组合抢答按钮信号,生成时钟脉冲。

- 清除功能:清除引脚(CLR)连接到一个总清除按钮,当按下时,将所有触发器复位,输出低电平,准备下一轮抢答。

- 输出与显示:输出引脚(Q0-Q3)连接到LED指示灯或数码管解码电路,用于显示抢答结果。例如,当某一路抢答成功时,对应输出高电平,点亮LED。

- 锁定机制:通过74LS171的边沿触发特性,第一个时钟上升沿锁存数据,确保后续按钮操作无效,直到清除信号复位。

四、工作过程详解

- 初始状态:清除信号有效,所有输出为低电平,指示灯熄灭。

- 抢答阶段:参与者按下按钮时,对应数据输入变为高电平。第一个按钮按下产生时钟上升沿,74LS171锁存该路数据,输出高电平并保持,同时指示灯亮起。

- 锁定与显示:一旦某一路被锁定,其他按钮按下不会改变输出,直到主持人按下清除按钮,系统复位。

五、优点与改进建议

本设计基于74LS171,具有结构简单、响应快、成本低的优点。TTL逻辑可能受噪声影响,建议添加去抖动电路(如RC滤波器或专用去抖动IC)以提高稳定性。可扩展为更多路抢答器,通过级联74LS171或其他逻辑器件实现。

六、总结

通过74LS171集成电路,四路抢答器设计实现了基本的抢答功能,突出了数字电路在现实应用中的实用性。该设计适合电子初学者学习和实践,可根据需求进一步优化,如添加声音提示或数字显示功能。掌握此类电路设计有助于深入理解时序逻辑和集成电路的应用。