电磁兼容性(EMC)浪涌保护电路在现代集成电路(IC)设计中至关重要,旨在防止瞬态电压事件(如雷击、开关操作)对电子设备造成损害。本文将从原理和设计两方面,探讨集成电路中的EMC浪涌保护电路。

一、EMC浪涌保护电路的基本原理

EMC浪涌保护电路的核心是响应瞬态过电压,将其能量导向安全路径,避免损坏敏感IC组件。浪涌通常指持续时间短(微秒至毫秒)、电压高(可达数千伏)的脉冲。在集成电路中,保护机制基于半导体器件的快速开关特性,常见原理包括:

1. 钳位原理:使用齐纳二极管或瞬态电压抑制器(TVS)将电压限制在安全水平。当浪涌电压超过阈值时,器件迅速导通,形成低阻抗路径,分流电流。

2. 能量吸收原理:通过电阻、电容或专用结构(如硅控整流器SCR)耗散浪涌能量,转化为热能。

3. 隔离原理:利用电感或变压器隔离高频浪涌,防止其传播到IC核心部分。

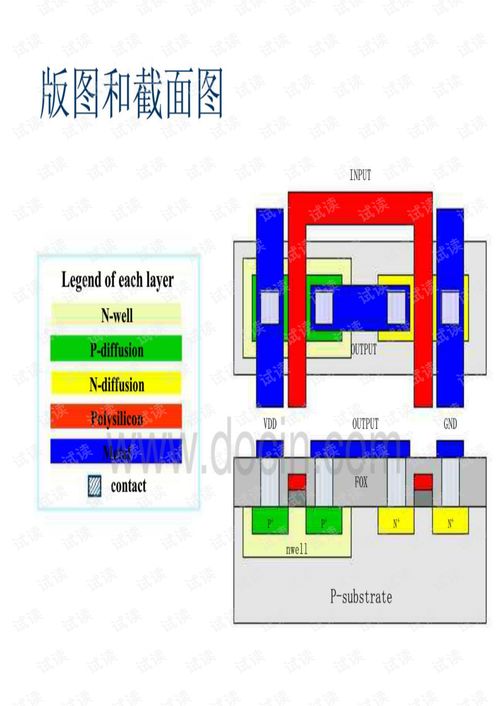

这些原理在IC设计中需结合工艺特性,例如利用CMOS工艺的寄生二极管或晶体管实现集成保护。

二、EMC浪涌保护电路的设计方法

在集成电路设计中,EMC浪涌保护需从系统级和器件级综合考虑,确保高性能、小面积和低成本。设计步骤如下:

- 需求分析:确定浪涌标准(如IEC 61000-4-5),包括电压峰值、波形(如8/20μs)和耐受等级。根据IC应用场景(如汽车、工业)设定保护目标。

- 拓扑选择:常见拓扑包括:

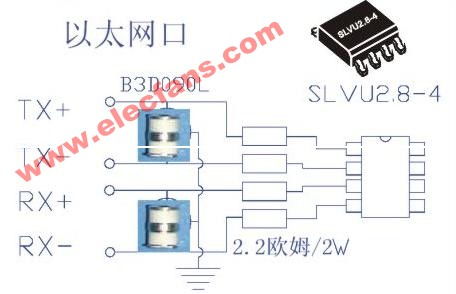

- 输入/输出(I/O)保护:在引脚处集成TVS或二极管钳位电路,防止静电放电(ESD)和浪涌。

- 电源保护:使用去耦电容和电压调节器,结合片上TVS,吸收电源线上的瞬态能量。

- 多级保护:串联电阻、电感和TVS,实现分级能量耗散,提高可靠性。

- 器件设计:利用IC工艺设计保护器件:

- TVS二极管:优化掺杂剖面和结面积,以实现低钳位电压和高能量处理能力。

- MOS基保护:设计栅极耦合或衬底触发结构,实现快速响应。

- 寄生元件利用:合理布局以减少寄生电感和电阻,避免性能下降。

- 仿真与验证:使用SPICE或专用EDA工具进行瞬态仿真,检查钳位电压、响应时间和热效应。通过实验测试(如浪涌发生器)验证设计,确保符合EMC标准。

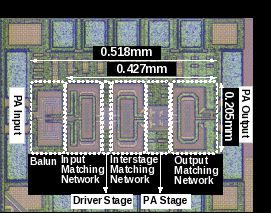

- 布局优化:在IC版图中,将保护电路靠近I/O焊盘,减少寄生效应;采用对称布局以均衡电流分布,避免局部过热。

三、设计挑战与未来趋势

IC中的EMC浪涌保护面临尺寸缩小、高频应用等挑战。例如,先进节点下,器件更易受浪涌损伤,需开发新型材料(如宽禁带半导体)。未来趋势包括智能保护电路(集成传感器和控制器)、系统级封装(SiP)集成外部保护元件,以及AI辅助设计优化。

EMC浪涌保护电路是集成电路可靠性的关键。通过深入理解原理并采用系统化设计方法,工程师可以有效提升IC的抗浪涌能力,满足日益严格的EMC要求。