数字集成电路版图设计是半导体芯片制造流程中的关键环节,它涉及将逻辑电路转换为物理布局的过程。本部分将重点介绍使用Cadence IC工具进行原理图绘制与仿真的基本流程。

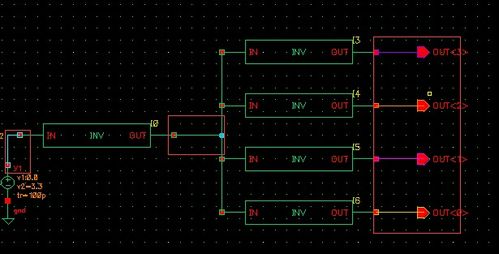

原理图绘制是集成电路设计的基础。在Cadence IC环境中,设计者通过图形界面绘制电路图,包括晶体管、电阻、电容等元件的连接。这一阶段需要严格遵循设计规范,确保电路逻辑正确。工具提供了丰富的库元件和连线功能,支持层次化设计,便于管理复杂电路。

仿真验证是确保电路功能正确的关键步骤。Cadence IC集成了仿真工具如Spectre或Virtuoso,允许设计者对原理图进行动态测试。通过输入激励信号,模拟电路在不同条件下的行为,包括时序、功耗和信号完整性分析。仿真结果可帮助识别设计错误,优化性能,减少后续物理实现的迭代次数。

原理图绘制与仿真是版图设计的前置工作,为后续布局布线提供可靠基础。掌握这一流程,能有效提升集成电路设计的效率与准确性。