引言

在第三代移动通信系统(3G)中,宽带码分多址(WCDMA)技术扮演着核心角色。作为WCDMA射频前端的关键模块,功率放大器(PA)的性能直接决定了系统的通信质量、覆盖范围和功耗水平。其集成电路(IC)设计,旨在将这一高性能模拟射频模块集成到单颗芯片上,是实现终端设备小型化、低成本和高效率的关键。本文将系统阐述WCDMA功率放大器集成电路设计的关键技术、核心挑战与主要实现路径。

一、 WCDMA功率放大器的核心设计要求

与恒定包络信号系统不同,WCDMA信号具有高峰均功率比(PAPR)的非恒定包络特性。这对PA设计提出了独特且严苛的要求:

- 高线性度:这是最核心的指标。必须严格控制频谱再生(如邻道泄漏比ACLR)和调制误差(如误差矢量幅度EVM),以确保信号质量并避免干扰相邻信道。

- 高效率:尤其在用户终端(UE)中,PA是主要的耗电单元。提高功率附加效率(PAE)和平均效率,对于延长电池续航至关重要。

- 足够的输出功率:需满足系统规范的功率等级要求,同时具备良好的功率控制能力。

- 宽动态范围:WCDMA的功率控制要求PA能在较大的功率范围内(通常超过80dB)保持线性工作。

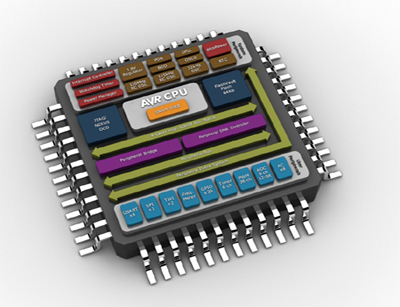

- 集成化与低成本:采用标准硅基工艺(如CMOS、SiGe BiCMOS)实现单片集成,以降低尺寸和成本。

二、 集成电路设计中的关键技术

为实现上述目标,现代WCDMA PA IC设计采用了多种先进技术:

- 线性化技术:

- 前馈技术:通过误差提取和抵消环路,能提供极高的线性度,但结构复杂、效率较低,多见于基站PA。

- 预失真技术:尤其数字预失真(DPD),通过在基带预补偿PA的非线性,是实现高线性与高效率平衡的主流方案,已广泛应用于射频IC中。

- 包络跟踪技术:根据输入信号的包络动态调整PA的电源电压,使PA始终工作在接近饱和的高效区,从而显著提升平均效率,是解决高峰均比信号效率问题的有效方法。

- 高效率电路架构:

- 异相(Outphasing/LINC)技术:将信号分解为两个恒定包络信号,分别通过高效饱和放大器放大后合成,兼具高线性与高效率潜力,但对路径匹配要求极高。

- Doherty放大器架构:通过主、辅放大器的负载调制,在回退功率区(如6dB)仍能保持较高效率,非常适合WCDMA信号统计特性,是移动终端PA最主流的架构之一。

- 先进半导体工艺:

- GaAs HBT:传统高性能射频PA工艺,具有高功率密度、高效率和高线性潜力,但集成度与成本受限。

- SiGe BiCMOS:在保持良好射频性能的实现了与CMOS逻辑电路的集成,是高性能集成PA的优选。

- RF CMOS:凭借极致的集成能力和低成本,在纳米工艺节点下,通过电路设计创新(如堆叠式晶体管、变压器合成等)正不断突破性能瓶颈,已成为中低功率集成PA的主流趋势。

三、 主要设计挑战与应对策略

- 线性与效率的权衡:这是最根本的矛盾。解决方案在于采用上述智能架构(如Doherty、包络跟踪)和线性化技术(如DPD),在系统层面进行协同优化。

- 热管理与可靠性:高集成度下的功率密度剧增,导致芯片温度升高,影响性能与寿命。需在版图设计时优化散热路径,采用热电协同仿真,并可能集成温度检测与保护电路。

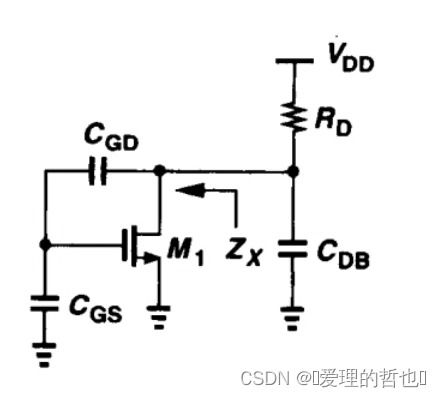

- 工艺波动与建模精度:深亚微米工艺的波动对模拟射频电路影响显著。设计必须考虑工艺角(Process Corner)和蒙特卡洛分析,并依赖于精确的器件PDK模型,特别是大信号非线性模型。

- 电源噪声抑制:包络跟踪等技术的引入使电源电压快速变化,极易通过衬底耦合和电源线干扰敏感电路。需要精心设计电源管理电路、电源滤波网络及隔离结构。

- 封装与测试:封装寄生参数(如键合线电感)会严重影响高频性能。需采用先进封装(如Flip-Chip、模塑封装)并实现封装-芯片协同设计。量产测试的成本和复杂性也是产品化的重要挑战。

四、 典型设计流程与实现路径

- 指标分解与架构选型:根据系统标准(3GPP)和终端需求,确定线性度、效率、输出功率等核心指标,并选择最合适的放大器架构和工艺技术。

- 晶体管级设计与仿真:进行偏置电路、匹配网络(输入/输出/级间)、稳定性电路的设计。利用EDA工具进行直流、小信号(S参数)、大信号(谐波平衡、瞬态)以及负载牵引仿真,优化性能。

- 版图设计与后仿真:射频版图需特别关注寄生效应、对称性、接地和电磁耦合。完成版图后必须进行包含所有寄生参数的提取和后仿真,以验证性能是否达标。

- 系统集成与验证:将PA核心与可能的集成式偏置控制、功率检测、模式切换等逻辑模块集成。进行芯片流片、封装和全面的测试验证,包括连续波测试和复杂的WCDMA调制信号测试。

结论

WCDMA功率放大器的集成电路设计是一个多目标、多约束的复杂优化过程,它深刻体现了射频模拟设计与数字通信系统需求的融合。随着5G乃至6G技术的演进,对更高频段、更宽带宽和更高能效的追求,将继续推动PA架构、线性化技术和集成工艺的创新。基于先进CMOS工艺,深度融合数字辅助与模拟电路设计的智能化、可重构PA,将是实现下一代无线终端高性能、高集成度与低功耗的关键所在。