在当今信息时代,数字集成电路(IC)构成了电子设备的核心,从智能手机到数据中心,无处不在。而硬件描述语言(HDL)作为连接抽象设计思想与具体物理实现的桥梁,在其中扮演着至关重要的角色。其中,Verilog HDL因其简洁的C语言风格、强大的建模能力和广泛的支持,已成为工业界与学术界进行数字系统设计的主流语言之一。《Verilog HDL数字集成电路设计原理与应用(第二版)》一书,正是系统学习和掌握这一关键技术的经典指南。

本书的核心内容紧密围绕数字集成电路设计的完整流程展开。它首先从Verilog HDL的基础语法入手,清晰地讲解模块(Module)、端口(Port)、数据类型(如wire、reg)、运算符及行为级建模(always、initial块)等基本概念。与第一版相比,第二版通常会更注重对最新语言标准(如IEEE Std 1364-2005)特性的阐释,并强化了对可综合代码风格(RTL级描述)的指导,确保设计能够被主流的综合工具有效地映射到目标工艺库。

在原理层面,该书深入探讨了如何利用Verilog进行组合逻辑与时序逻辑的建模。读者将学会如何描述多路选择器、编码器、寄存器、计数器以及有限状态机(FSM)等基本数字电路模块。更重要的是,本书将设计原理与硬件思维相结合,强调代码风格对最终电路面积、速度和功耗的影响,引导读者避免常见的建模陷阱,如锁存器的无意生成、仿真与综合的不匹配等。

“应用”是本书的另一大重点。它超越了单纯的语法教学,系统地介绍了基于Verilog的现代数字IC设计方法学。这包括:

- 层次化设计与模块化方法:如何构建复杂系统的层次结构,实现设计复用。

- 测试平台的构建:详细讲解如何编写验证用的testbench,包括时钟生成、激励施加、响应监控和结果自动比对,这是保证设计功能正确的关键。

- 可综合设计与设计约束:深入讲解如何编写能被综合工具理解的RTL代码,并初步引入时序约束的概念,为后端物理设计奠定基础。

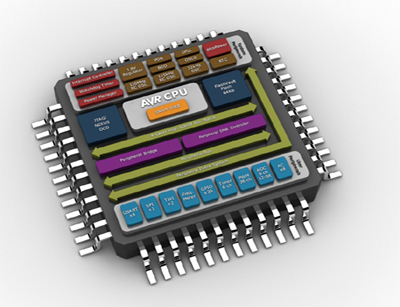

- 设计案例研究:通过CPU子系统、通信接口(如UART)或数字信号处理(DSP)单元等实际案例,将分散的知识点串联起来,展示从规格定义、模块划分、Verilog编码、功能仿真到初步综合的完整项目流程。

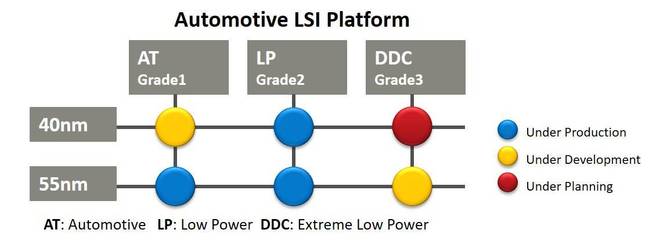

第二版通常会根据技术发展,增加或强化对前沿设计方法和挑战的讨论,例如低功耗设计技术(时钟门控、多电压域)、面向可测性设计(DFT)的基本概念,以及使用Verilog进行简单FPGA原型验证的流程简介。这些内容使读者不仅掌握语言工具,更能理解工业级芯片设计的全貌。

总而言之,《Verilog HDL数字集成电路设计原理与应用(第二版)》不仅仅是一本Verilog语法手册,更是一部贯通设计原理、工程实践与前沿方法的综合性教程。它为电子工程、微电子等相关专业的学生和初入行业的工程师提供了坚实的理论基础和实践指引,是踏入数字集成电路设计殿堂的一把宝贵钥匙。通过系统学习,读者能够建立起从软件描述到硬件实现的思维范式,为参与高性能处理器、高速通信芯片、智能AI加速器等尖端集成电路的研发工作做好充分准备。